Semiconductor Packaging Industry Overview

Plus Information on Latest Investment Analysis and Pick

Hi Everyone,

This newsletter provides an overview of the semiconductor packaging equipment market. The information contained here was included in the detailed company analysis that I performed on Kulicke & Soffa (KLIC) that was sent to paid subscribers. In addition to the full investment analysis, which included the detailed financial model that I built as part of the process, that report also contained a full update and overview of what is occurring in the semiconductor chip and equipment market. Most of you have probably heard of the shortages, I provide insights into the current state of the shortages and the expected path forward based on the views of industry insiders.

If you would rather just read the KLIC investment analysis or even just the full industry report contained in it, you can purchase either on my website through this link. To be clear, the industry update is all included in the KLIC report. I am simply giving people the option to purchase it separately.

If you are wondering why I am only including these reports for paid subscribers / putting them behind a paywall, I think you would understand after seeing the level of detail and inferring the number of hours that go into just one report. But, it is a virtuous cycle. More paid subscribers provide me with more bandwidth to use resources that allow me to confirm unique insights that make for a great investment. I am not going to tout how “successful” this pick has been and the return since I made the recommendation for paid subs. Rather, I hope that recipients of these reports are continuing to develop a robust analytical framework for investing in the public markets.

With that, please make sure to share this newsletter, share this post, or subscribe (if you have not already) if you like the content! You can use the buttons here to do so:

Industry Overview

Packaging Introduction

The figure above shows where KLIC sits in the semiconductor value chain; Semiconductor Manufacturing Equipment – providing equipment and tools to Assembly, Test, and Packaging (“ATP”) and Fabrication companies. The slowdown (or end) of Moore’s Law has brought the previously low-value back-end of the supply chain to the forefront. Packaging has become a bottleneck to progress in the semiconductor industry; meanwhile, the industry has begun to utilize packaging techniques to continue improving overall performance. People think of Moore’s Law as increasing chip transistor densities; the rule of thumb being an exponential doubling every 18-24 months. While transistor densities have historically accelerated higher, chip interconnects advanced at a relatively more sluggish pace.

I’ll briefly clarify the difference between transistors and interconnects. Transistors can be amplifiers or switches, the latter of which enables a binary “on” or “off” state. Transistors are organized into “logic gates” to allow computers to store information and make decisions. Interconnects do as they sound, connect transistors and other electronic components to each other, making them functional. The analogy provided by Semiconductor Engineering equates interconnects to a highway. Just as the speed at which you can drive depends on how packed the highway is, so does chip speed depend on how fast signals and power can move around the chip. So, as the quantity of transistors has increased, chip speed has been suppressed because of the lack of sufficient interconnect technologies.

Moore’s Law has served as a guiding beacon for the industry for over 50 years (which was led by Intel for the majority of that time). However, with the rate of increasing transistor densities slowing dramatically due simply to boundaries created by physics, the industry has pivoted to focusing on Advanced Packaging (“AP”) techniques to drive advancements in performance, power consumption, and form factors. There is value to learning the history of packaging, which is helpful for understanding where the industry is moving. While I will cover the essential properties, Mule on Twitter wrote a great primer on the history of packaging. Mule is who pointed me in the direction of KLIC, so big hat tip to him! You can watch this video for a great overview of the current and future state of electronic engineering. It is not necessary for understanding packaging, but extremely helpful to understand the macro landscape.

I wanted to conclude this introduction with a point of fact. Moore’s Law by its classical definition is ending. However, in the same paper that launched “Moore’s Law” he said,

It may prove to be more economical to build large systems out of smaller functions, which are separately packaged and interconnected. The availability of large functions, combined with functional design and construction, should allow the manufacturer of large systems to design and construct a considerable variety of equipment both rapidly and economically.

Gordon Moore, “Cramming more components onto integrated circuits”

What is Semiconductor Packaging?

How would I explain packaging to a five-year-old? Packaging is the process of enclosing the chip (wafer) in protective material and serves two main purposes. First, the package protects the physical silicon and interconnects from either corrosion (which occurs when metal gradually breaks down due to chemical/electrochemical reactions when it interacts with its outside environment) or other physical damage. Second, packaging is the means by which a chip is connected to other chips or components, specifically a circuit board. These connections allow for electricity to flow to and from chips/components, which ultimately allows a device to function. Packaging material was originally ceramic but has since moved predominantly to laminate for cost and form-factor improvements. Ultimately, the packaging industry is seeking to optimize the balance between 1) size (form-factor), 2) power dissipation, and 3) cost. This write-up will not cover all the different packaging types since there are thousands of variations.

While it directly affects the power, performance, and cost at a high level, packaging also influences basic chip functionality. Due to its increasing importance, as well as the nature of modern (and future) packaging designs, packaging is no longer an after-thought. Rather, packaging is now contemplated as part of the front-end design and test processes. This has positive implications for both Electronic Design Automation (“EDA”) and Outsourced Semiconductor Assembly and Test (“OSAT”) companies. However, IDMs and Foundries are actively bringing assembly and test functions in-house; creating competition on the service side while expanding the potential customer base for equipment companies.

Why It is Important

Packaging was historically an enigma to the chip industry. It was viewed by engineers as just increasing the size (footprint) and cost of chips while decreasing the electrical conductivity. However, packaging provides the benefit of enabling connectivity between a chip and a printed circuit board (“PCB”); it makes system layout and assembly much easier. An often overlooked benefit of packaging is its ability to dissipate heat produced by the silicon die resulting from its processing functions.

I alluded to the fact that packaging is no longer taking a passive role in advancing overall semiconductor technology. While limits on transistor density is the commonly cited headwind for the industry’s ability to maintain progress in faster processing speeds, the bigger issue has become interconnect (the pathways that connect everything). Interconnect (the “wires”) account for over 50% of the path delay in modern chips. This is why the industry is now focused on packaging; pushing the envelope of advanced packaging (“AP”) methodologies, and adopting heterogeneous integration (“HI”). The path forward will continue to rely on fitting more functionality onto the chip and minimizing the space in which this can be accomplished.

Chip design costs are accelerating, seemingly exponentially. So, cost reduction has become a central area of focus among participants. The graph below stops at 5nm, if we extrapolate out to 3nm and below then costs start to get out of control. From SemiEngineering, “Generally, IC design costs have jumped from $51.3 million for a 28nm planar device to $297.8 million for a 7nm chip and $542.2 million for 5nm, according to IBS. But at 3nm, IC design costs range from a staggering $500 million to $1.5 billion, according to IBS. The $1.5 billion figure involves a complex GPU at Nvidia.” Aside from pure functionality, packaging innovation will need to be a core component of the cost-reduction solution.

The Evolution of Packaging: Then and Now

Since the first semiconductor was packaged in 1965, the industry has focused on innovating on two fronts: higher pin count and smaller form-factor (“footprint”). Of course, Fairchild created the first commercial packaging technology with Dual In-line Package (“DIP”), which consisted of two separate rows of pins that served as the connectivity medium. Packaging innovation evolved as transistor density (quantity of gates on each chip) increased, it had to. As transistor density increased, I/O and total pin count increased, which required packaging to accommodate the additional connections between the chip and external components/circuit board. The industry’s solution was the Pin-Grid Array (“PGA”) and Ball-Grid Array (“BGA”) packaging designs to address the growth in data and address busses (connection lanes) that are the means by which data is transferred in and out of a chip resulting from advanced SoCs.

As solutions for increased pin counts were solved, the focus shifted towards reducing the packaging footprint. Chip Scale Packages (“CSPs”) were the next innovation to address higher pin counts and smaller form-factors. This development was just in time for the proliferation of smartphones, laptops, and other smaller electronic devices; the race for geometry scaling/shrinkage was a necessity. Packaging has to follow suit. The “near die size” paradigm had customers demanding packages that added no or little incremental footprints to the die. With the transistor density scaling issues mentioned above, packaging is becoming the instrument through which industry participants are attempting to keep pace with the spirit of Moore’s Law – increasing processing speed for the same footprint size. The two new paradigms driving this effort forward are advanced packaging and heterogeneous integration.

The Basics

Before reviewing AP and HI, there are some important concepts to understand.

Interconnection Methods

Wire Bond: Wire bonding consists of interconnection between the die and packaging using wires. Historically gold used to be the standard, but copper started taking over as the preferred material due to cost and connectivity. It is the most cost-effective and flexible type of interconnection. It is reliable and simple, an attractive combination for a basic chip. Wire bonding is primarily used for low-cost legacy packages, midrange packages, and memory die stacking. There are a few wire bonding techniques:

Ball Bonding: A sphere (“ball”) is formed at the end of the wire which is connected to the pad and the wire then extends vertically from the pad. Since the wire is sticking up, it can be extended in any direction so that any necessary connection can be made.

Wedge Bonding: Pressure is applied to the wire to press it against the pad. Unlike ball bonding, wedge bonds need to be aligned (using aligning tools) since the wire has to point in the direction of where the other bond is being made.

Stud/Bump Bonding: Similar to ball bonding, bumps are created for interconnection. However, instead of using wires, the balls sit right on the surface and attached directly to its corresponding component.

Thermosonic Bonding: Thermal + ultrasonic energy is used to connect components.

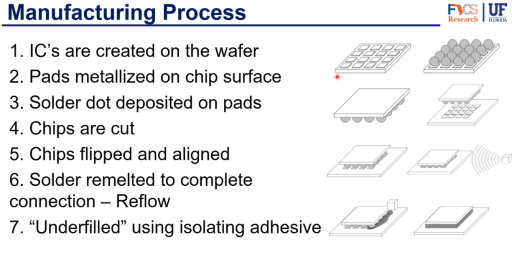

Flip Chip: Flip-chip packaging utilizes small solder bumps located on pads (which are located on the chips) to connect components. The chip is then flipped over so that the top faces down towards the substrate. The pads on the chip are aligned with pads on the substrate and the connection is made. Compared to wire bonding, the flip-chip method has a smaller footprint and higher density of interconnects than the wire bonds, resulting in more bandwidth and better performance due to shorter interconnects. This is a more expensive process than wire bonding, but is most likely a better option for more advanced chips given the superior performance.

Interposer: A (most often) silicon layer between a substrate and dies. It is both a package and a conduit used in multi-chip dies or boards to pass electrical signals to other chips in a package and to I/O ports. Think of the interposer as an electrical bridge connecting one chip or component to another. This reduces the need for long thin wire connectivity and thus the electrical resistance, so an interposer yields better performance and power efficiency. The silicon interposer has higher bandwidth and performance compared to the other two methods since the interconnections are shorter. There are two different interconection types:

Through-Silicon Via (“TSV”): A vertical interconnect that is drilled and passes through the silicon substrate (the interposer). TSVs enable 3D/multi-die stacking by reducing the interconnect length, which as I mentioned above, optimizes the flow of electrical current (lowers resistance). They make the vertical interconnection between the substrate and dies, carrying power and/or information. The issue engineers have encountered with TSVs is the inability to scale with higher (clock speed) frequencies.

Redistribution Layer (“RDL”): The very top layer of the interposer that makes horizontal connections between the various dies, pins, and TSVs. The RDLs re-route the information and power to where they need to be so that connections are made to the correct pins.

Bridge: Bridges are used as in-package interconnects for multi-die packages to connect one die to another through the interposer.

Interposers are used in heterogeneous integration due to the ease by which it can connect multiple chips and components to each other.

Substrate: The base in a package that is a component of most packaging, including advanced packaging, processes. The substrate connects the chip to the board in a system and consists of multiple layers, each of which incorporate metal traces and TSVs. The substrate also features routing layers that provide the electrical connections from the chip to the board and other components.

Advanced Packaging

As I mentioned above, Advanced Packaging can be viewed as a continuation of Moore’s Law and is necessarily correlated. Specifically, packaging techniques can amplify the incremental progress of transistor density. Ironically, wire (interconnect) length growth must accompany transistor shrinkage, which increases the distance over which an electrical signal must travel to go from one side of a chip to another. The lower the process node, the longer the total wire length, the longer it takes for electrical signals to travel from one part of the chip to another. This speed problem can be alleviated by widening the pathways through which the signals travel. Back to the earlier example, it is like adding more lanes to the highway to reduce traffic. The common tools the industry has adopted include Through-Silicon Vias (TSVs), interposers, bridges, and others. By reducing the space over which the electrical signals need to travel, the signals travel faster (boosts processing speed) and it requires less energy. When you start thinking about how cell phones, tablets, and other devices are getting smaller, yet faster, it is a result of increased functional density (“doing more with less”). Package designs will continue to evolve to accommodate increased density and I/O connectivity. To be clear, single-die (monolithic) packages will persist, but multi-die packages will be the solution for cost control and improved functionality for higher-end semiconductor technologies. Below I will briefly cover some of the popular Advanced Packaging types and methods before getting into the heart of the industry analysis. But first, there are some common structural components that need to be understood.

Aside from the power, performance, and form factor improvements provided by AP, the different packaging methods also enabled applicability to other markets and use-cases. Most importantly, these new designs enable heterogeneous integration: combining different types and quantities of processors, memory, and other components onto a single substrate. It may be obvious, but I wanted to emphasize the point, this allows for different chips (both digital and analog) at different process nodes to be combined together (known as a “chiplet”). This provides both a higher yield and easier die testing. The result is more specialization and flexibility. However, these benefits also come with cots.

Higher Complexity: Complexity brings not only higher costs but also difficulties for metrology, inspection, and testing to ensure all components of the more interconnected chip is working correctly.

Specialization: On one hand, greater specialization enables the spread of advancing semiconductor technology to a wide range of end-markets. However, the lack of standardization prevents volume scaling and the (cost) benefits that come with it.

Commercialization: Related to the lack of standardization, the chip industry has relied on massive scale to bring chip types at different nodes to market. It may be more difficult to commercialize these chips without the same scale experienced in the past.

System-in-Package (“SiP”)

SiP consists of combining two or more integrated circuits inside one or more packages. This is different from System-on-Chip (“SoC”), in which the functionality of different chips are all integrated on a single die. The different chip types can include digital, analog, and radio frequency (“RF”) chips. However, like SoC, SiP systems can perform all or most of the functions of an entire electrical system. While SiP has been around since the 1980s, the tighter integration and closer proximity of components achieve cost and speed improvements. Note that the interconnection inside the package is usually achieved through wire bonding. Wire bonding is essentially when the internal package components are connected with thin wires (previously made of gold, but moved to copper in the early 2010s), which are bonded to the package. SiP can also utilize a flip-chip methodology for interconnection, which utilizes solder bumps to connect chips. Combining processors, memory, storage, and other components enables smaller form factor and efficiency. A key benefit of SiP compared to SoC is the higher yield, which is critical for manufacturers as costs rise – thus generating a higher ROIC.

System-on-Package (“SoP”): SiP is evolving to SoP, in which passive components will actually be embedded in the substrate (package). This will once again increase density and/or minimize form factor. More components leads to more functionality which results in better performance and capabilities.

Fan-out wafer-level packaging (FOWLP) is at the forefront of the industry for consumer electronics products. FOWLP yields a smaller form factor due to its substrate-less package and higher performance due to the shorter interconnects and direct IC connection. greater complexity comes greater cost. One such variation of WLP is the Embedded Wafer-Level Ball Grid Array (eWLB), developed by Infineon in 2007. While flip-chip packages require an interposer layer to connect the I/O signal leads on the chip to the I/O “balls” soldered on the PCB, WLP requires no such layer. However, I/O pin counts in traditional WLP were limited to the area of the chip – but eWLB solved that problem. This packaging process consists of:

Known Good Dies (“KGD”) are placed face-down on a carrier wafer

The carrier wafer is covered in an epoxy mold, which forms a reconstituted wafer

The reconstituted wafers are processed to form RDLs

Bumps are placed on the uncovered side of the wafer for “fan-out” redistribution

Finally, the reconstituted wafer is diced – already packaged.

Heterogeneous Integration

Heterogeneous integration is the future of chip architecture and design, enabled by advanced packaging. HI is really the embodiment of “More than Moore” – increasing the functional density by integrating various components into a device so the whole is greater than the sum of its parts. The movement is driven by power, performance, area, and cost (“PPAC”); seen by lower power consumption, footprint, and latency coupled with higher speed and bandwidth. Scaling is still a component of HI; specifically, shrinking interconnects, bump pitch (width), TSVs, and bond pads. This all drives the need for advances in equipment/tools and metrology (test). This quote from an eetimes article sums up HI nicely (emphasis mine).

By HI, he does not mean homogeneously integrated SoCs, Systems-in-Package (SiPs), or Multi-Chip Modules (MCMs). Lu views HI as “a holistically integrated approach” that involves system design, algorithms, and software, together with different types of silicon dice such as SoC, DRAM, flashes, A-to-D/D-to-A, power management, security, and reliability control dices.

Nicky Lu, CEO and Founder of Etron Technology

We can create this heterogeneous integration that allows us to put the chips into a system and input completely different kinds of chips, whether it’s analog, mixed signal, digital, or even sensors. Die partitioning can improve yield, and the ability to integrate high-bandwidth memory and the ability to re-use various IP and reduce the power is key for integration.”

Yin Chang, senior vice president at ASE

Increased I will discuss three concepts to explain HI: chiplet architectures, 2.5D Chip Design, and 3D Chip Design.

Chiplet Architectures: Chiplets are built by integrating multiple dies into a single package or system. The approach the industry is taking is to provide a “library” of modular chips; the chips are then assembled and interconnected in a package. While this may sound like an SoC, there is an important difference. SoCs are built and scaled by advancing to lower nodes. As an example, an SoC would combine a CPU, memory, and 50 other IP components on a single die at a particular node. The only way to advance is by scaling the geometry to the next node – quite expensive and difficult. All of the different chips must be scaled accordingly. However, with chiplets, those different components can be pieced together separately. It is like going to a buffet and only choosing the exact pieces you need. These chiplets can then be reused at lower nodes. Think about it like an upscaled version of MacGyver. The obvious benefits of chiplets are the faster assembly time and lower cost compared to SoC. What excites me is the potential to combine chips from different IP vendors, which would require coordination among the design companies and software compatibility.

2.5D Chip Design: I was a bit mixed-up when trying to understand the difference between SiP and 2.5D until I read this article – feel free to read it at your leisure. The main difference between 2D SiP and 2.5D is that 2.5D packages utilize the silicon interposer (discussed above), and TSVs, to connect the substrate and the dice. The dice are attached to the interposer with micro bumps and the interposer is connected to the package substrate using flip-chip bumps. As can be seen, dies can be placed both horizontally and vertically with the interposer providing connectivity between the chips. 2.5D has become increasingly popular for high-end ASICs, FPGAs, GPUs, and memory components.

2.5D is not just the next step towards 3D packaging, it has many advantages on its own. First, these packages are smaller than traditional methodologies and feature shorter interconnections. Shorter interconnections yield higher processing speeds and lower overall power usage due to less resistance. While 3D packaging shows promise for higher overall densities, heat management becomes an issue (discussed further below). Alternatively, 2.5D has better heat management, making heterogeneous integration easier to accomplish.

However, with advanced technologies comes a higher required level of expertise in order to integrate all of these different components. An issue I see is the potential for longer lead times for planning and execution due to the higher overall complexity. It does seem that the EDAs (Cadence and Synopsis) are building the appropriate tools to accommodate advanced packaging, but these systems will need to continue to evolve to match the hardware requirements.

3D Chip Design: 3D packaging is the logical eventuality of this technology. Advanced packaging is moving to where NAND has already gone – 3D. 3D ICs consist of multiple dies stacked on top of each other, which presents a thermal issue since the heat generated by the chips would end up melting the chips. TSVs are located on the chips themselves, which connect the bottom chip to the top chip and the top chip to the substrate. Since all connections are done on the chip, 3D packaging is the fastest, most efficient, and complex methodology. Samsung first introduced 3D architectures with its 3D NAND product in August 2013. NAND flash could no longer be scaled in width and length on the chip. Since there was no more 2D space to increase density, the industry went vertical. This completely changed the narrative in the memory industry, as lithographic scaling was no longer the limiting factor. Now cost and performance improvements were not reliant just on horizontal scaling, but rather both horizontal and vertical scaling.

If you can lay down a horizontal series of control gates, then run a vertical series of floating gates and a channel that responds to those gates, then you can build strings that may be several cells long in the same area as a single planar cell.

https://thememoryguy.com/what-is-a-3d-nand/

Difficulties and Issues

Some of the developments in Advanced Packaging also present a variety of issues that the industry must account for.

Customization enabled by heterogeneous integration diminishes the scalability of process design kits (“PDKs”) and other off-the-shelf capabilities. As mentioned below, the industry will have to find a balance between scale and customization to ensure cost and efficiency benefits.

Inspection, metrology, and testing may prove a lot more difficult as these tools must navigate the integration of multiple and different types of chips, especially as different products scale at different rates. This especially applies to the analog market, which doesn’t benefit from geometry scaling. Chiplet architectures should alleviate some of those issues but may make certain components of the chip difficult to access.

Minimizing average total cost may prove difficult if specialization reduces the number of chips produced for a specific design or process. A theme that is starting to emerge is specialty packaging processes developed by fabs themselves, all reducing standardization and the associated cost benefits the industry has experienced historically.

This article did a nice job providing a holistic look at these and other issues presented by Advanced Packaging.

As a reminder, you can get a full semiconductor industry update or the entire Kulicke & Soffa analysis by either 1) signing up for the paid newsletter or 2) buying either on my website. I hope you found this overview of the semiconductor assembly market informative and interesting.

Hi Chris, great article, super helpful. One link seems to be missing though: "You can watch this video for a great overview of the current and future state of electronic engineering."