Kulicke & Soffa (KLIC) - Investment Pitch and Analysis (Part II)

Part II: Packaging Leader to Benefit from Equipment and Chip Shortage

Part II continues below…

Please make sure to share this newsletter, share this post, or subscribe (if you have not already) if you like the content! You can use the buttons here to do so:

DISCLAIMER:

All investment strategies and investments involve the risk of loss. Nothing contained in this website should be construed as investment advice. Any reference to an investment's past or potential performance is not, and should not be construed as, a recommendation or as a guarantee of any specific outcome or profit.

Industry Analysis

Market Structure and Value Chain

Value Chain

Analyzing a company’s value chain consists of analyzing a company’s discrete activities to deliver its product or service to the market. This informs a company’s ability to capture and/or sustain a competitive advantage. This type of analysis is applicable to vertically integrated companies or those that are susceptible to technological change. The latter applies to K&S, as technological changes can cause value chains to breakdown and allow companies to specialize in a narrower set of activities. This framework was obtained from Expectations Investing, by Al Rappaport and Michael Mauboussin. The overall analytical framework defined in this book has become the foundation of my company analysis and valuation.

Customer Priorities: KLIC has shown the ability to define its customer needs and meet those needs. The company has successfully navigated customer transitions from traditional to advanced packaging processes. A situation can occur in which companies exceed customer needs, allowing customers to shift priorities to lower prices or easier deliver methodologies (among other things), shifting the industry landscape. However, advanced packaging is an emerging paradigm in which customers continuously demand more innovation. K&S is well positioned to meet its customer’s priorities in the current and future environment.

Distribution Channels: The company delivers its equipment, tools, and services either directly to OSATs and IDMs or through a variety of distribution partners. As IDMs and foundries continue to carve out market share in advanced packaging, Kulicke & Soffa’s flexible delivery model will allow it to continue capitalizing on advanced packaging’s growing share of this part of the market. Additionally, KLIC has demonstrated the ability to scale production quickly and efficiently, most recently seen by its ability to ramp its production capacity to meet the high level of demand for its equipment.

Product Offering: Tying back to customer priorities, it must be apparent that the company delivers a product and solution that meet customer priorities. K&S is the leader in wire bond equipment, which is the method used for 80% of all semiconductor packages. Its customer relationships have only improved recently as they have passed some margin on to its customers through lower ASPs. This will come back to benefit the company when the next downturn comes.

Inputs/Raw Materials: K&S has developed strong relationships with its vendors, evidenced by previously winning customer of the year awards for some of its suppliers. The company’s unsolicited comments on its dedication to its suppliers align with comments made by certain suppliers. From when its Dutch subsidiary won the 2017 Dutch Industrial Supplier & Customer Awards (DISCA) (out of 243 nominees), “Kulicke & Soffa Netherlands B.V. received the top category accolade following a rigorous round of evaluation, including the company’s openness about cost, price, and forecast. Suppliers valued K&S for its willingness to share technology, knowledge, and trust while advocating suppliers’ competencies. Most importantly, the Company encourages a close partnership environment between suppliers and customers.“

Assets/Core Competency: K&S continues to be focused on capitalizing on its core competencies, providing industry-leading interconnect solutions since its founding 70 years ago in 1951. The company is acutely aware of its competitive positioning and technological advantage, only entering markets that require interconnect expertise.

Competitive Strategy

Porter’s Five Forces is an appropriate lens to analyze the Wafer Fabrication Equipment (“WFE”) due to its 1) defined boundaries, 2) relatively predictable patterns, and 3) physical capital orientation. Kulicke & Soffa (“K&S”) is a leader in the Assembly Equipment market, a sub-market of WFE.

Barriers to Entry / Durability of Competitive Advantage

It is very difficult for a new company to enter the Assembly Equipment market. A company will require a significant amount of start-up capital to build out manufacturing facilities and procure the materials required to build the equipment. As a result, economies of scale are required to distribute the high fixed costs. Aside from PP&E, companies need domain expertise and engineering talent to develop solutions that meet end-market needs and enable higher-intensity packaging solutions. K&S has reached the $1B revenue run-rate, which it states is the sustainable level of scale to consistently achieve its target of +20% operating margin.

Threat of Substitutes

Wire bonding will be a mainstay in packaging technology for the foreseeable future according to industry experts. Wire bonding is a cheaper alternative to flip-chip and interposer interconnection, so it will be the solution for lower-cost chips not requiring cutting-edge speed and efficiency. As an upper-management employee* at JCET Group (3rd largest OSAT) said in response to a comment that wire bonding will always be around, “Absolutely. It stays with the OSAT. Now the thing is when a large customer, a large IDM or OEM is interested to get the best deal from an OSAT is to do all their packages and all their tests, not just one type of package.” However, traditional wire bonding is a relatively commoditized, low-margin business. This makes advanced packaging mix important for the packaging vendors since it carries much higher margins. K&S reports that 40% of their wire bonding business is for advanced packaging; that mix should continue moving higher.

*Note: I had to exclude the actual title for confidentiality

Buyer Power

There are three possible categories of buyers for Assembly Equipment companies: Outsourced Semiconductor Assembly & Test (“OSAT”) companies, Foundries/IDMs, Distributors. There are three large OSATs – ASE, Amkor, and JCET – with about six others material players. There is no need to go into detail on the foundries and IDMs, but it should be known that these companies are becoming a larger part of the company’s potential customer base. Specifically, TSMC would be around the fourth largest provider of packaging services if its business was broken out separately. The quantity of buyers yields little buyer power. The commoditized nature of traditional wire bonding is beneficial for buyers, however advanced packaging wire bonding, flip-chip, and thermo-compression carry higher intensity and can be more specialized. A higher mix of advanced packaging business gives KLIC more power.

Supplier Power

There is little supplier power given the broad applicability of the components used to build the company’s equipment. The material and components the company procures equipment ranging from drive motors, positioning systems, precision components, and more. The supplier base consists of large global companies to smaller local ones. KLIC has a great relationship with its suppliers, evidenced by winning best customer awards.

Competitive Rivalry

K&S primarily competes with ASM Pacific Technology. BE Semiconductor Industries entered the assembly packaging space in 2009 with its acquisition of ESEC, but the rest of the industry is comprised of smaller players. ASM had always lagged K&S until around 2010 when the industry started transitioning from gold to copper wiring. Today, ASM competes with K&S in the lower-end wire bonding market, which carries lower margins, and customers can be somewhat indifferent between the equipment. However, KLIC is the leader among OSATs and dominates the higher-end wirebonding market being used in advanced packaging.

Business Model

Kulicke & Soffa operates in the Semiconductor Capital Equipment (“Semicap”) market. Companies in this market can experience volatility in quarterly results while maintaining a positive long-term trajectory. Performance is leveraged to the broader chip industry cycle, as customers (Foundries, IDMs, and OSATs) base their purchasing patterns based on their outlook of future demand. When demand is expected to outpace supply and cause tightened utilization rates, equipment and tool orders increase. Alternatively, if companies foresee excess capacity then they will reduce the magnitude and quantity of purchase orders (“PO”). This cyclicality serves as a short-to-intermediate term risk for Semicap companies.

Technological advancements in integrated circuits (“ICs”) are the catalyst for Semicap demand, as chip manufacturers require more advanced equipment and tools to continue meeting customer demands for leading-edge products. As chip complexity increases and the designers and manufacturers continue trying to shrink chip geometries, for at least the next 5-10 years, the equipment and machinery required to create these chips also increase. This equipment will garner higher prices but also requires Semicap companies to continuously invest in R&D and tangible capital to improve or maintain its competitive positioning. The most important thing to understand for a Semicap company is how its product line is positioned in the market. The companies that develop leading-edge equipment that meet direct customer needs have the ability to carve out a meaningful position in the supply chain.

The front-end equipment makers will benefit from the usage of larger diameter wafers coupled with a move to more automation, both phenomena result in more expensive node process lines for manufacturers. These higher expenditures provide upside for the front-end. On the back-end, geometry scaling makes testing and packaging more complex, which will yield higher margins for equipment providers. Packaging equipment companies specifically benefit from the industry’s move to copper interconnects due to the better connectivity and thus performance and power usage it provides. However, copper is more difficult to work with than gold or aluminum which were used historically. The higher level of difficulty requires more specialized and precise tools, which provide an opportunity for packaging companies to differentiate themselves.

In addition to broader chip cyclicality, businesses in the space incur risk of poor returns on incremental investments if R&D efforts prove fruitless or they lag behind better technologies produced by competitors. Close collaboration with customers can somewhat mitigate this risk, so customer service can be a subtle differentiator for Semicap companies. It’s critical that companies maintain a steady cadence of R&D and CapEx spend.

There are three primary metrics that can indicate business quality: Bookings, Book-to-Bill ratio, and industry-wide chip manufacturing utilization %. Intuitively, bookings should trend higher. The Book-to-Bill ratio, calculated as period order dollars divided by period sales, is an especially important metric to consider, as it indicates whether the business is expanding or contracting. Bookings precede sales, so a ratio above 1.0 will indicate higher future sales. Chip capacity utilization rates provide a benchmark for overall industry demand but are especially important for Semicaps due to the correlation between manufacturer utilization % and equipment bookings. Higher utilization rates indicate the need to expand capacity, which results in higher equipment order volumes.

Market Opportunity and Dynamics

The Assembly Equipment market has historically been cyclical along with most of the semiconductor industry. Specifically, there is a high correlation between chip unit shipments and company performance. However, three market dynamics are setting up a multi-year bull cycle for the overall semiconductor and packaging equipment companies. I will first cover the overall industry dynamics and trends then turn to industry participants to illustrate what is actually occurring in the value chain.

General Semiconductor Industry

The overall market grew in 2020 despite COVID headwinds and the resulting supply chain disruptions. Semiconductor Applications Forecaster (part of IDC) reported that global semiconductor sales grew by 5.4% to $442B in 2020 despite the COVID headwinds. In my view, 2020 was set up for growth coming out of the 2019 cyclical downturn, but achieving growth given the macroeconomic landscape was impressive nonetheless. Broken out separately, DRAM and NAND grew 4% and 32.9%, respectively. IDCs 2021 forecast from February 2021 calls for 7.7% growth in chip sales to $476B. I see multiple tailwinds that are often discussed for the broader industry including 5G networks, Internet of Things (“IoT”), and Artificial Intelligence (“AI”), which are all still nascent in their overall development and will require a step-wise increase in processing intensity. IDC provided some information on their overall 2020 breakdown and 2021 forecast, which I have somewhat reverse-engineered here:

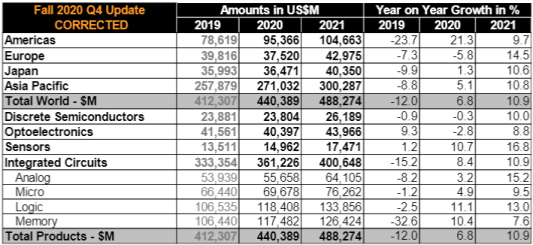

In mid-March, 1.5 months after IDC released its forecast, Worldwide Semiconductor Trade Statistics (“WSTS”) released the final 2020 chip sales figures along with its 2021 forecast. The image below is sourced from WSTS, revealing a breakdown by chip category. There are apparent differences between the two data sources, I lean towards WSTS. The organization reported 6.8% sales growth in 2020 to $440B; logic and memory led the industry last year. The expected acceleration in 2021 sales is a result of the supply constraints and chip shortages emanating from COVID disruptions and the aforementioned macro tailwinds. Total chips sales are expected to grow 10.9% above 2020 to $488B. The impact of IoT can be seen by sensors and analog chips leading the way this year.

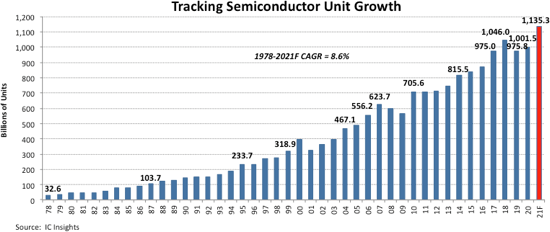

In addition to total sales, tracking unit shipments is critical to understanding the performance of certain areas of the value chain – including, assembly equipment. The chart below from ICInsights displays annual IC unit shipments since the late 1970s, representing an 8.6% CAGR over that time period. I received the updated 2021 forecast containing actual 2020 shipments today (great timing). So, if I miss any edits of the unit shipment counts for 2021 in this write-up, remember that 2021 growth is expected to be 13.4%

Shipments accelerated from 2000-2007, fueled by the rise of the Internet until the global financial crisis (“GFC”) led to a cyclical decline in IC shipments in 2008 and 2009. Coming out of the GFC, smartphones had started taking hold, and unit shipments spiked by 25% in 2010, surpassing 705 billion devices. Another sharp increase of 12% occurred in 2017, which brought total shipments near one trillion, which the industry achieved in 2018. The expected acceleration in 2021 is in line with all of the commentary I have received from those in the industry and jives with the high fab utilization rates.

Shipments can also be viewed through the lens of total area shipped, measured in millions of square inches (“MSI”). Total wafer area shipments in 2020 increased by over 5% to 12.4 billion square inches over 11.8B in 2019. While not a direct indicator of the number of units shipped, semi.org’s forecast of record-high MSI shipment in 2022 with continued growth thereafter is another data point supporting overall industry growth.

Semiconductor Capital Equipment (“Semicap”)

Total sales of semiconductor manufacturing equipment reached $59.6B in 2019 and are expected to have grown by 15.6% in 2020 to $68.9B according to SEMI. Strong growth in 2020 is expected to continue into 2021 and 2022, reaching $71.9B and $76.1B, respectively. The Semicap market can be bifurcated between the “Front End” and “Back End”; the Front End accounts for ~70% of the market with the Back End making up the remainder. Front End equipment relates to fabrication equipment, including photolithography, deposition, etching, cleaning, ion implantation, etc. Back End refers to assembly, packaging, and testing equipment. Kulicke & Soffa sits in this back-end, which is merging with the front-end. Separately, MarketsandMarkets forecasts the Semicap market to grow at a 9% CAGR through 2025, reaching $95.9B.

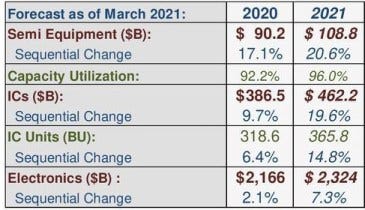

Wafer fab equipment (wafer processing, fab facility, photomask/reticle equipment) is estimated to have grown by 15% to reach $59.4B in 2020. This segment is expected to grow by 4% and 6% in 2021 and 2022, respectively. Foundry and logic account for ~50% of this market, as equipment churn/incremental spend is driven by the need to update facilities and processes with leading-edge equipment. NAND flash equipment stands out with 30% growth in 2020 (+$14B), with DRAM equipment expected to be the leader in 2021 and 2022. Separately, on March 16, 2021, SEMI reported a 16% increase in fab equipment spending in 2020, with continued robust growth expected for 2021 and 2022 resulting from “pandemic-inspired demand for electronic devices.” 2021 forecasted equipment spend is expected to increase by 15.5% in 2021 followed by slight deceleration in 2022 to 12%. This should equate to roughly $10B/year on incremental spend, reaching ~$80B by 2022.

The Test equipment market is also expected to grow by 20% in 2020, reaching $6B. This market is also expected to experience healthy growth through 2022 due to demand from 5G and HPC end-markets. Assembly and Packaging equipment is “forecast to grow 20% to $3.5 billion in 2020, followed by 8% and 5% increases in 2021 and 2022, respectively, driven by advanced packaging applications.” VLSI is forecasting 10% growth in packaging equipment for 2021, with the market reaching $4.4B in 2023. Overall market trends provide a bullish backdrop for Kulicke & Soffa’s business as the leader in advanced packaging. The upside for the company is in the advanced packaging trends, which the company is starting to execute with its various design wins. The entire Semicap market is poised for robust growth for the next three years, with assembly equipment primarily driven by increasing utilization of advanced packaging solutions.

Semicap / SME companies’ performance is correlated to front-end CapEx spending. Historically, capital expenditures have followed periods of high fabrication capacity utilization as fabs and IDMs are forced to expand operations to meet demand. Fabrication capacity utilization will usually run above 80% in periods of high demand, with individual fabs running between 90%-100%. Capacity utilization above 90% is a key indicator of oncoming manufacturing expansion, which is a leading indicator for Semicap demand. However, adding capacity is a lengthy process due to the complexity of the plants and process lines in addition to the capital intensity. Connecting the dots between current high utilization and proliferating chip demand across industry verticals, fabs/IDMs will have to build out significantly more capacity in the oncoming years. This spending will filter down throughout the value chain, which is discussed further below.

Advanced Packaging Market

ResearchandMarkets estimates that the global Advanced Packaging market will grow from $29.4B in 2019 to $73.4B in 2027, representing a 12.1% CAGR. Detail on the AP technologies and demand drivers are provided below. The semiconductor industry must develop advanced packaging technologies to continue advancing chip performance, power, and size. Physical limitations and quantum mechanical dynamics serve as a cap on geometry scaling. Advanced Packaging provides a solution by building performance-enhancing capabilities into the package itself. As a result, the packaging process has moved from the back-end, as an afterthought, to the front-end and part of the overall design process. As a result, foundries and IDMs are starting to build out their own packaging capabilities – fighting for market share with OSATs. EET Asia provides a quote that encompasses the AP trend (emphasis mine):

“A new era of advanced packaging is at our doorstep. From advanced flip-chip and fan out technologies, now new and more advanced technologies are needed for assembly of double-sided SiP, as well new TCB and hybrid bonding solutions for complex heterogeneous packaging are required. This in combination with different carriers for Known Good dies (trays, TnR, reconstructed wafer) and other interposers (wafer, panel, substrate) opens opportunities for new, innovative and cost-effective, equipment that offer very high accuracy, high yield, and high speed. We see the demand for equipment that offers solutions to these industry demands growing strongly and have a clear focus on supplying such solutions in a timely way.”

Ruurd Boomsma, BESI’s CTO comments

The same tailwinds supporting the broader chip market apply to advanced packaging. Advanced Packaging is mostly used for the mobile and consumer markets currently, due to the smaller form factor. In addition to these trends, the need for more power-efficient consumer electronics and advanced chip architectures will be specific demand drivers for advanced packaging. However, there remains a possibility that OSATs and manufacturers will try to delay the transition to advanced packaging for as long as they can due to the higher initial and maintenance costs associated with AP. With that being said, the transition to advanced packaging for the high-end market is an inevitability (my opinion) as transistor scaling continues. Conversations with industry experts reveal that traditional wire bonders were priced around $60,000, but the “steppers” used for interconnect today cost “a few million dollars.“

Current State of the Industry

General Semiconductor Industry

All of the indicators I have been seeing indicate that 2021 and 2022 will be big years for the chip industry and specifically equipment companies. The last thing you all need is another take on the current chip shortage, the impact of which is being felt through many areas of the economy. Analyzing the confluence of factors is helpful to understand the inner workings of the global supply chain; however, it is more useful to look forward. The path forward starts with the current state of the industry. While the current backlog is partially a result of the demand shock resulting from consumer electronics sales and the work-from-home (“WFH”) paradigm, future demand will be heavily driven by AI, 5G, and IoT proliferation. This positive demand environment can be juxtaposed to the current and worsening long-term supply dynamics resulting from the difficulty of geometry scaling and increasing chip complexity discussed throughout this report. All of this points to a cyclical bull market within a secular bull market.

The latest industry data shows current capacity utilization of 96% as of March 2021, which makes sense given the aforementioned chip shortage. Fabrication capacity utilization is the percentage of the total available capacity that is used at a given time. IDMs and foundries are trying to catch up on a massive backlog of orders and have ramped production in response. In line with the market dynamic above, Taiwan Semiconductor (“TSMC”), Intel, Samsung, and others are announcing record levels of forthcoming capital expenditures (referenced below). However, even producing at 96% of capacity won’t bring market supply and demand into balance until some time in 2022. Techspot reports that Harlan Sur (J.P. Morgan analyst) estimates that supply is currently outpacing demand by 10-30%. He expects this imbalance to persist for the next three or four quarters; however, the situation wouldn’t be resolved at that point. The industry will need an additional one or two quarters before inventories reach normal levels. Piecing this all together results in a normalized market at some point in 2022.

Semiconductor fabrication capacity utilization has been trending higher since the beginning of 2019 and the start of a cyclical downturn for the industry. Utilization has been steadily rising, seasonally adjusted, since then except for the drop off in Q1 2020 due to COVID. But ramping utilization takes time due to process complexity and specialization of knowledge and equipment required for production. According to SIA, there can be up to 1,400 process steps to manufacture the wafer; each requires using highly sophisticated tools and machines. This results in a chip manufacturing process that takes up to 26 weeks, SIA explains:

Manufacturing a finished semiconductor wafer, known as the cycle time, takes about 12 weeks on average but can take up to 14-20 weeks for advanced processes. To perfect the fabrication process of a chip to ramp-up production yields and volumes takes even much more time – around 24 weeks. Then, once the fabrication process is complete, the semiconductors on the silicon wafer need to go through yet another stage of production known as back-end assembly, test, and package (ATP), before the chips are final and ready for delivery to the end customer. ATP can take an additional 6 weeks to complete. Therefore, the lead time, which is from when a customer places an order to receiving the final product, can take up to a total of 26 weeks. The table below provides some average times required in the chip fabrication process.

Semiconductor Industry Association

However, even if the industry continues operating at near 100% capacity, the current supply/demand imbalance has caused a 16-week lead time (time between order placement and order delivery) in March based on reporting from Bloomberg. This is the highest lead time since 2018, which has been categorized as the “danger zone” for inventory levels. It’s difficult to see this dynamic improving any time soon. Following the demand shock caused by the rapid growth in consumer electronic purchases resulting from the WFH movement, there is oncoming demand from the economic recovery throughout 2021. Coupled with continued headwinds on the supply side, including supply chain disruptions and idiosyncratic events (e.g. Samsung fab shutdown in Texas, Renesas fab fire), the forecast of a normalized by mid-2022 seems reasonable. Matthew Sheerin from Stifel also mentioned higher material costs as another constraint on supply.

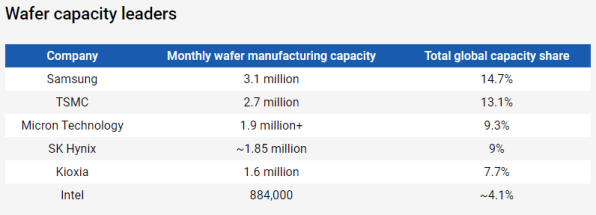

Even while running at above 90% capacity, inventory destocking relative to demand can be seen in the chart below. Inventory levels have come down slightly (in line with comments throughout the industry) and look to have stabilized but billings continue to move higher. This paints a picture of demand continuing to outpace supply. Rob Thubron states, “Exacerbating the issue has been the increasingly complex manufacturing process making chips more difficult to produce, the larger number of chips in every device, logistical problems, and package shortages. The China/US trade war saw companies trying to stockpile chips in advance, putting further pressure on manufacturers.” As a result, wafer manufacturers will need to keep up with high production levels and expand capacity. The current capacity picture can be seen below:

Semiconductor Packaging Market

Structural Changes – Advanced Packaging

Chip manufacturers are developing their own packaging/back-end solutions. As an example, TSMC developed leadership in the space by developing a leading-edge advanced packaging platform for its customers. These solutions include fan-out (InFO) to 2.5D Si interposer (CoWoS), to 3D SoIC, all of which contribute to their 3rd or 4th place positioning among OSATs for just its packaging business. But it is important to point out that TSMC and other foundries will only provide advanced packaging solutions, not traditional packaging like wire bonding. Wire bonding will always have a presence in the industry but will stay with the OSATs. Due to the commoditized nature of traditional wire bonds, OSATs could be relatively indifferent to the equipment they used; allowing these customers to play the equipment providers off each other. K&S noted the resulting lower margins on its traditional wire bonding business. This provided a better overall pricing environment for the OSATs, which was helpful given the low margins. However, since advanced packaging is involved on the front-end and much more complex than traditional methods, the pricing environment is also different.

“And the thing is that people couldn’t realize that if you offload Moore’s law into packaging, packaging has to cost more. There are examples where the packaging is extreme examples, too, but the packaging cost more than the silicon.”

JCET Group Manager, Interview

Industry insiders are confident in advanced packaging’s continued and growing role given broader technological advancements and the capabilities AP provides. The same JCET Group manager commented, “So 6G used to be the millimeter-wave with 150 gigahertz operations. So the future product, they will all be based on very advanced packaging because you need AI accelerators, image processors. You need high bandwidth memory, processors. So CPU, 64 gigahertz products modem for millimeter-wave modem, 5G, 6G.“

While the wire bonding outlook in the medium term is very bullish, the industry also believes that there is a structural “new normal” coming due to increased competition. This will be in light of the industry adding significant capacity over the next two to three years as is expected. The competitive landscape may lead to further consolidation following ASE’s acquisition of SPIL, which was formerly the fourth largest OSAT.

Recent Underinvestment

In addition to the growing prevalence of advanced packaging, Kulicke & Soffa will benefit immensely from what I believe is an oncoming increased investment in wire bonding resulting from previous years of underinvestment in wire bond capacity. An interview with ASE (#1 OSAT; KLIC #3 customer) illuminated the opportunity for Kulicke & Soffa (emphasis mine):

ASE is pretty consistent. But in terms of wire bond, we haven’t added a ton of wire bond capacity because the margins weren’t that good. Years ago, and again, I think Amkor came back and retooled a lot of their lead frame-based packages to larger chip sizes and stuff, the high matrix tooling and stuff where they could become more profitable. And that worked out well for them for a while because they captured a lot of the wire bond, because a lot of this stuff isn’t going anywhere… You can do a flip chip to your fan or some different packages, but you’re going to pay more. So no one’s added capacity in the last couple of years without contributing to price right now.

I think we’ve got over 1,200 wire bonders on the order. We’re adding 10% in Q1 (2021), 8% in Q2 (2021). So we are expanding wire bond capacity. But we’re doing it because we have loading commitments and long-term commitments from our customers. So wire bond capacity is pretty fungible. You can use it for a QFN or you can use it for an SLIC. So there’s not a huge amount of risk.

ASE, Interview

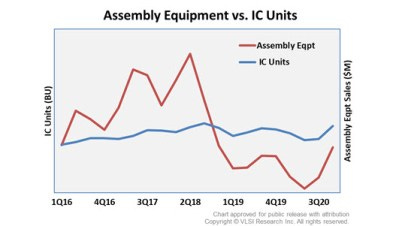

Given that assembly equipment sales are correlated to IC unit shipments, the recent underinvestment makes sense a priori. However, this is a critical claim that needs to be verified. The graphic below shows how leveraged assembly equipment sales are to integrated circuit unit shipments. Investment in assembly equipment experienced a deep decline in 2019 as the semiconductor market experienced a trough in its industry cycle. The bear market in 2019 was followed by COVID in 2020, a further drag on IC shipments and thus equipment sales. Underinvestment the past two years has created capacity constraints, creating a scenario that should result in rapid sales growth over the next one to two years. The result has been a wirebonding shortage unlike anything industry participants have seen in 20 years, expanded on below.

ASE spent ~$1.6 billion on capacity expansion in 2020; a lot of which was for wire bond with the majority for advanced packaging. To further that point, ASE group COO Tien Wu stated that the company “will see its wire-bonding capacity run at full utilization and remain short of demand through the end of 2021, and up to 90% of clients have signed two-year contracts for capacity support.” This underinvestment and oncoming spend by ASE is actually an industry-wide phenomenon, as noted by ASE’s COO on their earnings call (emphasis mine):

However, given the 2020 capacity crunch, I believe all of our competitors are placing order for all of the equipment that are required to meet customer demand.

Dr. Tien Wu, COO of ASE Technology Holding – Q4 2020 Earnings Call

Shortages and Long Lead Times

The structural changes and recent underinvestment in wire bonding, coupled with the spike in demand over the past year, have led to a wire bond shortage. This massive shortage puts K&S in an even more important position in the overall value chain. This is the biggest shortage in at least 20 years, as mentioned below (emphasis mine):

I’m sure you’ve probably heard that right now, there’s a huge worldwide wire bond shortage. That’s just insane. I’ve never seen it in 20 years in the industry where customers weren’t getting enough wire bond.

ASE, Interview

ASE elaborated on the state of the wirebonding market in their latest earnings call. Note the confirmation of 1,200 wire bond additions from the interview comment above, except the COO states that the 1,200 is only confirmed delivery. They want to double their capacity this year but are reliant on the machinery lead times, from K&S:

The first question is the demand has not slowed down at all. And the machinery lead time is getting longer. That’s why we’re confident that the wire bonder capacity will remain to be tight to the end of this year, at least, if not longer. In terms of the number of wire bonders we’re adding, I think last year we have 1800 (additions), and this year we believe we will add to similar number of units. Right now we have confirmed delivery of 1200. And we’re working on the other. In terms of the wirebonder tightness…is a combination of demand has not slowed down, as well as machine lead time. And it’s not just wire bonder, its the whole line balance.

Dr. Tien Wu, COO of ASE Technology Holding – Q4 2020 Earnings Call

Dr. Tien side-stepped a question that directly referenced K&S, but confirmed that the long lead times apply to many of their vendors and equipment used. In ASE’s Q3 2020 earnings call, the company estimated that the wire bond shortage would persist through Q2 2021. It is now extending this expectation through the end of 2021 at a minimum. They also increased the machinery delivery lead time (how long they have to wait) from 6-8 months to 6-9 months, the environment is not improving yet.

Amkor (#2 OSAT) has echoed the same message as ASE, as Amkor’s VP of wirebond BGA products stated, “We are seeing capacity tight pretty much across the board.” To focus only on wire bonds would be missing the bigger picture; shortages are seen in manufacturing capacity, certain packaging types, key components, and equipment. The equipment shortage means more orders for Kulicke & Soffa, specifically its two main business lines. The spot shortages in packaging began to emerge in late 2020; both wirebond and flip-chip capacity is expected to remain tight through 2021. In addition to the tight capacity, delivery lead-times for wirebonders and other equipment have stretched further. Lead frames and substrates are also in short supply and are core components used in packaging.

Given that wire bonding accounts for 75%-80% of all packaging today, based on interconnect methodology, KLIC should be one of the primary beneficiaries of the current market environment. Even when the market stabilizes in 2-3 years, the increased proportion of memory dies that are stacked will continue to drive demand for advanced wire bonding services. ASE stated in the Q3 2020 conference call, “in this particular cycle, it’s not just the volume. It’s also the number of dies, the number of wires, as well as the complexity.”

Flip-chip mounting is also experiencing above-average demand as an advanced packaging process. Amkor expects flip-chip capacity to continue running at a high level of utilization through 2021, with equipment lead times “greater than 2x what we typically experience.” Roger St. Amand, Sr. VP at Amkor, elaborates that “Based on available forecasts, we expect this trend to continue through 2021, and into 2022, driven by higher demand in the communications, computing, and automotive market segments. In general, we are seeing this trend across all flip-chip package technologies.”

Demand Drivers

In summary, the semiconductor capital equipment market demand, on the whole, is driven by upstream capital expenditures, among other things. Rapid buildouts of new foundries and foundry expansions to add broader industry capacity require more and cutting-edge tools. Most recently, Intel announced its plan to invest $20B to build two leading-edge fabs in Arizona, both expected to go online by 2024. Not to be outdone, on March 31st Taiwan Semiconductor announced that it plans to invest $100B in just the next three years to expand capacity. All of this CapEx is revenue for Semicap companies. DRAM content required by the automotive end-market and a proliferating consumer electronics market, driven by 5G, provide two additional tailwinds. Capital intensity and complexity will only continue as geometry scaling continues to be a goal within the industry and supplemented by advanced packaging technologies to keep pushing the limits of IC functionality. Finally, demand for semiconductor chips in the form of more intensive computational power, connectivity, and memory requirements will persist for many years due to growth in AI, edge network, and server applications.

Industry Overview

Packaging Introduction

The figure above shows where KLIC sits in the semiconductor value chain; Semiconductor Manufacturing Equipment – providing equipment and tools to Assembly, Test, and Packaging (“ATP”) and Fabrication companies. The slowdown (or end) of Moore’s Law has brought the previously low-value back-end of the supply chain to the forefront. Packaging has become a bottleneck to progress in the semiconductor industry; meanwhile, the industry has begun to utilize packaging techniques to continue improving overall performance. People think of Moore’s Law as increasing chip transistor densities; the rule of thumb being an exponential doubling every 18-24 months. While transistor densities have historically accelerated higher, chip interconnects advanced at a relatively more sluggish pace.

I’ll briefly clarify the difference between transistors and interconnects. Transistors can be amplifiers or switches, the latter of which enables a binary “on” or “off” state. Transistors are organized into “logic gates” to allow computers to store information and make decisions. Interconnects do as they sound, connect transistors and other electronic components to each other, making them functional. The analogy provided by Semiconductor Engineering equates interconnects to a highway. Just as the speed at which you can drive depends on how packed the highway is, so does chip speed depend on how fast signals and power can move around the chip. So, as the quantity of transistors has increased, chip speed has been suppressed because of the lack of sufficient interconnect technologies.

Moore’s Law has served as a guiding beacon for the industry for over 50 years (which was led by Intel for the majority of that time). However, with the rate of increasing transistor densities slowing dramatically due simply to boundaries created by physics, the industry has pivoted to focusing on Advanced Packaging (“AP”) techniques to drive advancements in performance, power consumption, and form factors. There is value to learning the history of packaging, which is helpful for understanding where the industry is moving. While I will cover the essential properties, Mule on Twitter wrote a great primer on the history of packaging. Mule is who pointed me in the direction of KLIC, so big hat tip to him! You can watch this video for a great overview of the current and future state of electronic engineering. It is not necessary for understanding packaging, but extremely helpful to understand the macro landscape.

I wanted to conclude this introduction with a point of fact. Moore’s Law by its classical definition is ending. However, in the same paper that launched “Moore’s Law” he said,

It may prove to be more economical to build large systems out of smaller functions, which are separately packaged and interconnected. The availability of large functions, combined with functional design and construction, should allow the manufacturer of large systems to design and construct a considerable variety of equipment both rapidly and economically.

Gordon Moore, “Cramming more components onto integrated circuits”

What is Semiconductor Packaging?

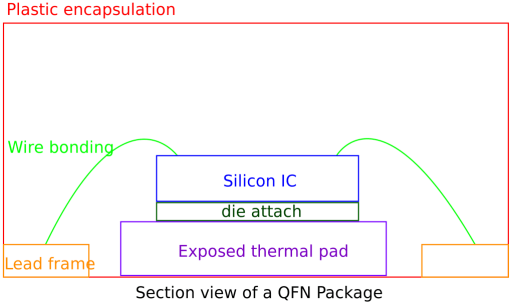

How would I explain packaging to a five-year-old? Packaging is the process of enclosing the chip (wafer) in protective material and serves two main purposes. First, the package protects the physical silicon and interconnects from either corrosion (which occurs when metal gradually breaks down due to chemical/electrochemical reactions when it interacts with its outside environment) or other physical damage. Second, packaging is the means by which a chip is connected to other chips or components, specifically a circuit board. These connections allow for electricity to flow to and from chips/components, which ultimately allows a device to function. Packaging material was originally ceramic but has since moved predominantly to laminate for cost and form-factor improvements. Ultimately, the packaging industry is seeking to optimize the balance between 1) size (form-factor), 2) power dissipation, and 3) cost. This write-up will not cover all the different packaging types since there are thousands of variations.

While it directly affects the power, performance, and cost at a high level, packaging also influences basic chip functionality. Due to its increasing importance, as well as the nature of modern (and future) packaging designs, packaging is no longer an after-thought. Rather, packaging is now contemplated as part of the front-end design and test processes. This has positive implications for both Electronic Design Automation (“EDA”) and Outsourced Semiconductor Assembly and Test (“OSAT”) companies. However, IDMs and Foundries are actively bringing assembly and test functions in-house; creating competition on the service side while expanding the potential customer base for equipment companies.

Why It is Important

Packaging was historically an enigma to the chip industry. It was viewed by engineers as just increasing the size (footprint) and cost of chips while decreasing the electrical conductivity. However, packaging provides the benefit of enabling connectivity between a chip and a printed circuit board (“PCB”); it makes system layout and assembly much easier. An often overlooked benefit of packaging is its ability to dissipate heat produced by the silicon die resulting from its processing functions.

I alluded to the fact that packaging is no longer taking a passive role in advancing overall semiconductor technology. While limits on transistor density is the commonly cited headwind for the industry’s ability to maintain progress in faster processing speeds, the bigger issue has become interconnect (the pathways that connect everything). Interconnect (the “wires”) account for over 50% of the path delay in modern chips. This is why the industry is now focused on packaging; pushing the envelope of advanced packaging (“AP”) methodologies, and adopting heterogeneous integration (“HI”). The path forward will continue to rely on fitting more functionality onto the chip and minimizing the space in which this can be accomplished.

Chip design costs are accelerating, seemingly exponentially. So, cost reduction has become a central area of focus among participants. The graph below stops at 5nm, if we extrapolate out to 3nm and below then costs start to get out of control. From SemiEngineering, “Generally, IC design costs have jumped from $51.3 million for a 28nm planar device to $297.8 million for a 7nm chip and $542.2 million for 5nm, according to IBS. But at 3nm, IC design costs range from a staggering $500 million to $1.5 billion, according to IBS. The $1.5 billion figure involves a complex GPU at Nvidia.” Aside from pure functionality, packaging innovation will need to be a core component of the cost-reduction solution.

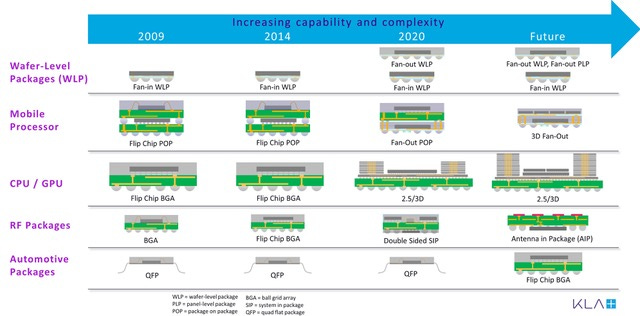

The Evolution of Packaging: Then and Now

Since the first semiconductor was packaged in 1965, the industry has focused on innovating on two fronts: higher pin count and smaller form-factor (“footprint”). Of course, Fairchild created the first commercial packaging technology with Dual In-line Package (“DIP”), which consisted of two separate rows of pins that served as the connectivity medium. Packaging innovation evolved as transistor density (quantity of gates on each chip) increased, it had to. As transistor density increased, I/O and total pin count increased, which required packaging to accommodate the additional connections between the chip and external components/circuit board. The industry’s solution was the Pin-Grid Array (“PGA”) and Ball-Grid Array (“BGA”) packaging designs to address the growth in data and address busses (connection lanes) that are the means by which data is transferred in and out of a chip resulting from advanced SoCs.

As solutions for increased pin counts were solved, the focus shifted towards reducing the packaging footprint. Chip Scale Packages (“CSPs”) were the next innovation to address higher pin counts and smaller form-factors. This development was just in time for the proliferation of smartphones, laptops, and other smaller electronic devices; the race for geometry scaling/shrinkage was a necessity. Packaging has to follow suit. The “near die size” paradigm had customers demanding packages that added no or little incremental footprints to the die. With the transistor density scaling issues mentioned above, packaging is becoming the instrument through which industry participants are attempting to keep pace with the spirit of Moore’s Law – increasing processing speed for the same footprint size. The two new paradigms driving this effort forward are advanced packaging and heterogeneous integration.

The Basics

Before reviewing AP and HI, there are some important concepts to understand.

Interconnection Methods

Wire Bond: Wire bonding consists of interconnection between the die and packaging using wires. Historically gold used to be the standard, but copper started taking over as the preferred material due to cost and connectivity. It is the most cost-effective and flexible type of interconnection. It is reliable and simple, an attractive combination for a basic chip. Wire bonding is primarily used for low-cost legacy packages, midrange packages, and memory die stacking. There are a few wire bonding techniques:

Ball Bonding: A sphere (“ball”) is formed at the end of the wire which is connected to the pad and the wire then extends vertically from the pad. Since the wire is sticking up, it can be extended in any direction so that any necessary connection can be made.

Wedge Bonding: Pressure is applied to the wire to press it against the pad. Unlike ball bonding, wedge bonds need to be aligned (using aligning tools) since the wire has to point in the direction of where the other bond is being made.

Stud/Bump Bonding: Similar to ball bonding, bumps are created for interconnection. However, instead of using wires, the balls sit right on the surface and attached directly to its corresponding component.

Thermosonic Bonding: Thermal + ultrasonic energy is used to connect components.

Flip Chip: Flip-chip packaging utilizes small solder bumps located on pads (which are located on the chips) to connect components. The chip is then flipped over so that the top faces down towards the substrate. The pads on the chip are aligned with pads on the substrate and the connection is made. Compared to wire bonding, the flip-chip method has a smaller footprint and higher density of interconnects than the wire bonds, resulting in more bandwidth and better performance due to shorter interconnects. This is a more expensive process than wire bonding, but is most likely a better option for more advanced chips given the superior performance.

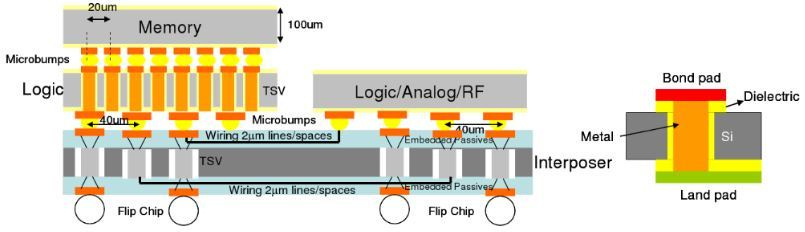

Interposer: A (most often) silicon layer between a substrate and dies. It is both a package and a conduit used in multi-chip dies or boards to pass electrical signals to other chips in a package and to I/O ports. Think of the interposer as an electrical bridge connecting one chip or component to another. This reduces the need for long thin wire connectivity and thus the electrical resistance, so an interposer yields better performance and power efficiency. The silicon interposer has higher bandwidth and performance compared to the other two methods since the interconnections are shorter. There are two different interconection types:

Through-Silicon Via (“TSV”): A vertical interconnect that is drilled and passes through the silicon substrate (the interposer). TSVs enable 3D/multi-die stacking by reducing the interconnect length, which as I mentioned above, optimizes the flow of electrical current (lowers resistance). They make the vertical interconnection between the substrate and dies, carrying power and/or information. The issue engineers have encountered with TSVs is the inability to scale with higher (clock speed) frequencies.

Redistribution Layer (“RDL”): The very top layer of the interposer that makes horizontal connections between the various dies, pins, and TSVs. The RDLs re-route the information and power to where they need to be so that connections are made to the correct pins.

Bridge: Bridges are used as in-package interconnects for multi-die packages to connect one die to another through the interposer.

Interposers are used in heterogeneous integration due to the ease by which it can connect multiple chips and components to each other.

Substrate: The base in a package that is a component of most packaging, including advanced packaging, processes. The substrate connects the chip to the board in a system and consists of multiple layers, each of which incorporate metal traces and TSVs. The substrate also features routing layers that provide the electrical connections from the chip to the board and other components.

Advanced Packaging

As I mentioned above, Advanced Packaging can be viewed as a continuation of Moore’s Law and is necessarily correlated. Specifically, packaging techniques can amplify the incremental progress of transistor density. Ironically, wire (interconnect) length growth must accompany transistor shrinkage, which increases the distance over which an electrical signal must travel to go from one side of a chip to another. The lower the process node, the longer the total wire length, the longer it takes for electrical signals to travel from one part of the chip to another. This speed problem can be alleviated by widening the pathways through which the signals travel. Back to the earlier example, it is like adding more lanes to the highway to reduce traffic. The common tools the industry has adopted include Through-Silicon Vias (TSVs), interposers, bridges, and others. By reducing the space over which the electrical signals need to travel, the signals travel faster (boosts processing speed) and it requires less energy. When you start thinking about how cell phones, tablets, and other devices are getting smaller, yet faster, it is a result of increased functional density (“doing more with less”). Package designs will continue to evolve to accommodate increased density and I/O connectivity. To be clear, single-die (monolithic) packages will persist, but multi-die packages will be the solution for cost control and improved functionality for higher-end semiconductor technologies. Below I will briefly cover some of the popular Advanced Packaging types and methods before getting into the heart of the industry analysis. But first, there are some common structural components that need to be understood.

Aside from the power, performance, and form factor improvements provided by AP, the different packaging methods also enabled applicability to other markets and use-cases. Most importantly, these new designs enable heterogeneous integration: combining different types and quantities of processors, memory, and other components onto a single substrate. It may be obvious, but I wanted to emphasize the point, this allows for different chips (both digital and analog) at different process nodes to be combined together (known as a “chiplet”). This provides both a higher yield and easier die testing. The result is more specialization and flexibility. However, these benefits also come with cots.

Higher Complexity: Complexity brings not only higher costs but also difficulties for metrology, inspection, and testing to ensure all components of the more interconnected chip is working correctly.

Specialization: On one hand, greater specialization enables the spread of advancing semiconductor technology to a wide range of end-markets. However, the lack of standardization prevents volume scaling and the (cost) benefits that come with it.

Commercialization: Related to the lack of standardization, the chip industry has relied on massive scale to bring chip types at different nodes to market. It may be more difficult to commercialize these chips without the same scale experienced in the past.

System-in-Package (“SiP”)

SiP consists of combining two or more integrated circuits inside one or more packages. This is different from System-on-Chip (“SoC”), in which the functionality of different chips are all integrated on a single die. The different chip types can include digital, analog, and radio frequency (“RF”) chips. However, like SoC, SiP systems can perform all or most of the functions of an entire electrical system. While SiP has been around since the 1980s, the tighter integration and closer proximity of components achieve cost and speed improvements. Note that the interconnection inside the package is usually achieved through wire bonding. Wire bonding is essentially when the internal package components are connected with thin wires (previously made of gold, but moved to copper in the early 2010s), which are bonded to the package. SiP can also utilize a flip-chip methodology for interconnection, which utilizes solder bumps to connect chips. Combining processors, memory, storage, and other components enables smaller form factor and efficiency. A key benefit of SiP compared to SoC is the higher yield, which is critical for manufacturers as costs rise – thus generating a higher ROIC.

System-on-Package (“SoP”): SiP is evolving to SoP, in which passive components will actually be embedded in the substrate (package). This will once again increase density and/or minimize form factor. More components leads to more functionality which results in better performance and capabilities.

Wafer-Level Packaging (“WLP”)

Instead of individual dies being packaged separately, all of the dies cut from a wafer are packaged while still on the wafer. The solder balls and RDL are actually built onto the wafer and dicing only occurs once the package is finished. The two different types of WLP are “Fan-In” and “Fan-Out” – with Fan-In being smaller than Fan-Out, but the latter offering more I/O. Due to the scale and holistic process, WLP is cheaper and more reliable than wire bonding. As a result, (for Fan-In) the form-factor shrinks relatively as the package for each die ends up being roughly the same size as the chip itself. Fan-In results in a package truly the size of the chip, Fan-Out results in a total package size larger than the die but more I/O connections in the mold surrounding the die. WLP results in greater I/O but is accompanied by significant manufacturing challenges due to the heat generated as part of the process and related fragility of the chip. Some of these issues include wafer warping and cracks in solder balls, both drastically harm the integrity of the package. WLP is optimal for 3D packaging and other applications requiring smaller form factors and higher performance.

Fan-out wafer-level packaging (FOWLP) is at the forefront of the industry for consumer electronics products. FOWLP yields a smaller form factor due to its substrate-less package and higher performance due to the shorter interconnects and direct IC connection. greater complexity comes greater cost. One such variation of WLP is the Embedded Wafer-Level Ball Grid Array (eWLB), developed by Infineon in 2007. While flip-chip packages require an interposer layer to connect the I/O signal leads on the chip to the I/O “balls” soldered on the PCB, WLP requires no such layer. However, I/O pin counts in traditional WLP were limited to the area of the chip – but eWLB solved that problem. This packaging process consists of:

Known Good Dies (“KGD”) are placed face-down on a carrier wafer

The carrier wafer is covered in an epoxy mold, which forms a reconstituted wafer

The reconstituted wafers are processed to form RDLs

Bumps are placed on the uncovered side of the wafer for “fan-out” redistribution

Finally, the reconstituted wafer is diced – already packaged.

Heterogeneous Integration

Heterogeneous integration is the future of chip architecture and design, enabled by advanced packaging. HI is really the embodiment of “More than Moore” – increasing the functional density by integrating various components into a device so the whole is greater than the sum of its parts. The movement is driven by power, performance, area, and cost (“PPAC”); seen by lower power consumption, footprint, and latency coupled with higher speed and bandwidth. Scaling is still a component of HI; specifically, shrinking interconnects, bump pitch (width), TSVs, and bond pads. This all drives the need for advances in equipment/tools and metrology (test). This quote from an eetimes article sums up HI nicely (emphasis mine).

By HI, he does not mean homogeneously integrated SoCs, Systems-in-Package (SiPs), or Multi-Chip Modules (MCMs). Lu views HI as “a holistically integrated approach” that involves system design, algorithms, and software, together with different types of silicon dice such as SoC, DRAM, flashes, A-to-D/D-to-A, power management, security, and reliability control dices.

Nicky Lu, CEO and Founder of Etron Technology

We can create this heterogeneous integration that allows us to put the chips into a system and input completely different kinds of chips, whether it’s analog, mixed signal, digital, or even sensors. Die partitioning can improve yield, and the ability to integrate high-bandwidth memory and the ability to re-use various IP and reduce the power is key for integration.”

Yin Chang, senior vice president at ASE

Increased I will discuss three concepts to explain HI: chiplet architectures, 2.5D Chip Design, and 3D Chip Design.

Chiplet Architectures: Chiplets are built by integrating multiple dies into a single package or system. The approach the industry is taking is to provide a “library” of modular chips; the chips are then assembled and interconnected in a package. While this may sound like an SoC, there is an important difference. SoCs are built and scaled by advancing to lower nodes. As an example, an SoC would combine a CPU, memory, and 50 other IP components on a single die at a particular node. The only way to advance is by scaling the geometry to the next node – quite expensive and difficult. All of the different chips must be scaled accordingly. However, with chiplets, those different components can be pieced together separately. It is like going to a buffet and only choosing the exact pieces you need. These chiplets can then be reused at lower nodes. Think about it like an upscaled version of MacGyver. The obvious benefits of chiplets are the faster assembly time and lower cost compared to SoC. What excites me is the potential to combine chips from different IP vendors, which would require coordination among the design companies and software compatibility.

2.5D Chip Design: I was a bit mixed-up when trying to understand the difference between SiP and 2.5D until I read this article – feel free to read it at your leisure. The main difference between 2D SiP and 2.5D is that 2.5D packages utilize the silicon interposer (discussed above), and TSVs, to connect the substrate and the dice. The dice are attached to the interposer with micro bumps and the interposer is connected to the package substrate using flip-chip bumps. As can be seen, dies can be placed both horizontally and vertically with the interposer providing connectivity between the chips. 2.5D has become increasingly popular for high-end ASICs, FPGAs, GPUs, and memory components.

2.5D is not just the next step towards 3D packaging, it has many advantages on its own. First, these packages are smaller than traditional methodologies and feature shorter interconnections. Shorter interconnections yield higher processing speeds and lower overall power usage due to less resistance. While 3D packaging shows promise for higher overall densities, heat management becomes an issue (discussed further below). Alternatively, 2.5D has better heat management, making heterogeneous integration easier to accomplish.

However, with advanced technologies comes a higher required level of expertise in order to integrate all of these different components. An issue I see is the potential for longer lead times for planning and execution due to the higher overall complexity. It does seem that the EDAs (Cadence and Synopsis) are building the appropriate tools to accommodate advanced packaging, but these systems will need to continue to evolve to match the hardware requirements.

3D Chip Design: 3D packaging is the logical eventuality of this technology. Advanced packaging is moving to where NAND has already gone – 3D. 3D ICs consist of multiple dies stacked on top of each other, which presents a thermal issue since the heat generated by the chips would end up melting the chips. TSVs are located on the chips themselves, which connect the bottom chip to the top chip and the top chip to the substrate. Since all connections are done on the chip, 3D packaging is the fastest, most efficient, and complex methodology. Samsung first introduced 3D architectures with its 3D NAND product in August 2013. NAND flash could no longer be scaled in width and length on the chip. Since there was no more 2D space to increase density, the industry went vertical. This completely changed the narrative in the memory industry, as lithographic scaling was no longer the limiting factor. Now cost and performance improvements were not reliant just on horizontal scaling, but rather both horizontal and vertical scaling.

If you can lay down a horizontal series of control gates, then run a vertical series of floating gates and a channel that responds to those gates, then you can build strings that may be several cells long in the same area as a single planar cell.

https://thememoryguy.com/what-is-a-3d-nand/

Difficulties and Issues

Some of the developments in Advanced Packaging also present a variety of issues that the industry must account for.

Customization enabled by heterogeneous integration diminishes the scalability of process design kits (“PDKs”) and other off-the-shelf capabilities. As mentioned below, the industry will have to find a balance between scale and customization to ensure cost and efficiency benefits.

Inspection, metrology, and testing may prove a lot more difficult as these tools must navigate the integration of multiple and different types of chips, especially as different products scale at different rates. This especially applies to the analog market, which doesn’t benefit from geometry scaling. Chiplet architectures should alleviate some of those issues but may make certain components of the chip difficult to access.

Minimizing average total cost may prove difficult if specialization reduces the number of chips produced for a specific design or process. A theme that is starting to emerge is specialty packaging processes developed by fabs themselves, all reducing standardization and the associated cost benefits the industry has experienced historically.

This article did a nice job providing a holistic look at these and other issues presented by Advanced Packaging.

Conclusion

This detailed overview of Kulicke & Soffa and the markets in which it participates reflects my view that the Comapny is still undervalued even after the recent 25% run in the stock over the past two weeks. Please do your own due diligence and reach out with any questions.